Ist der einzige Zweck von Transistoren in einer CPU, als Schalter zu fungieren, die ihren Befehlssatz definieren? Und wenn ja, warum erhöht dann die Erhöhung der Anzahl der Transistoren die Geschwindigkeit?

Wie erhöht das Erhöhen der Anzahl von Transistoren in einem Chip seine Geschwindigkeit?

Antworten:

Aus dem Kopf:

Mehr Cache , schneller als RAM

Mehr SIMD-Anweisungen , die schneller verarbeitet werden als Einzeldatenanweisungen

Mehr Kerne , sodass Sie zwei oder mehr Dinge gleichzeitig erledigen können

Weitere Funktionseinheiten, wie Einbau- FPU s, und mehrere ALU s

Pipelines , sodass jeder Kern mehr Dinge gleichzeitig tun kann

Bessere Verarbeitungslogik, wie komplexere Verzweigungsvorhersagelogik

Wenn Sie neugierig auf solche Dinge sind, empfehle ich das Buch The Elements of Computing von Noam Nisan und Shimon Schocken (zumindest in der ersten Hälfte). Nachdem Sie es durchgearbeitet haben, können Sie Ihre eigene Frage detailliert beantworten und die beteiligten Teile genau kennen.

Die Companion-Website enthält einige Beispielkapitel und -notizen. Es ist ein sehr zugängliches Buch. Ich habe es ohne Probleme alleine durchgearbeitet und dann eine brandneue Klasse an meiner Universität besucht, die es als Haupttext verwendete.

Die einfache Antwort ist, dass mehr Transistoren den Rest nicht schneller machen , aber anstatt eine Sache pro Zeitraum zu tun, können wir jetzt zwei machen (mit einigen Einschränkungen).

Ken hat bereits einige Gründe in seiner Antwort zusammengefasst . Um das weiter auszubauen

- Mehr Cache , schneller als RAM

Offensichtlich benötigen größere Caches mehr Transistoren. Mit mehr Transistoren haben wir aber auch die Wahl, schnellere Caches zu verwenden . CPU-Caches sind nur SRAMs, die typischerweise aus 6 Transistoren (AKA 6T SRAM) bestehen. Wenn jedoch genügend Transistoren vorhanden sind, kann es sich lohnen, schnellere, aber größere SRAM-Zellen zu verwenden, die aus mehr als 6 Transistoren bestehen (z. B. 8T, 10T SRAM).

- Mehr SIMD-Anweisungen , die schneller verarbeitet werden als Einzeldatenanweisungen

Nicht nur SIMD, sondern jede Art von Beschleunigungsanweisung. Beispielsweise verfügen moderne Architekturen häufig über eine AES-Einheit für eine schnellere Verschlüsselung / Entschlüsselung, eine FMA für eine bessere mathematische Berechnung (insbesondere digitale Signalverarbeitung) oder eine Virtualisierung für schnellere virtuelle Maschinen. Wenn Sie mehr Anweisungen unterstützen, sind mehr Ressourcen erforderlich, um sie zu dekodieren und auszuführen

Diese sind ziemlich klar

In der Vergangenheit gab es nicht genügend Chipfläche für die FPU, so dass die Leute eine separate kaufen müssen, wenn sie hohe Anforderungen an die Gleitkomma-Arithmetik haben. Mit deutlich mehr Transistoren kann die FPU eingebaut werden, was die Gleitkomma-Mathematik erheblich beschleunigt

Außerdem sind moderne CPUs superskalar und versuchen, mehrere Dinge gleichzeitig zu tun, indem sie unabhängige Datenstücke finden und diese früher berechnen, obwohl der Befehlsstrom linear und seriell ist. Je mehr Dinge sie parallel tun können, desto schneller werden sie. Zu diesem Zweck kann eine CPU mehrere ALUs und eine ALU mehrere Ausführungseinheiten haben. Wenn eine CPU beispielsweise 5 Addierer hat, verglichen mit 4 in der vorherigen Generation, läuft sie in der optimistischsten Situation bereits 25% schneller, ohne dass sich die Uhr ändert. Anspruchsvollere CPUs verwenden sogar eine Ausführung außerhalb der Reihenfolge (was bei den meisten modernen Hochleistungs-CPUs der Fall ist).

Operationen können normalerweise auf verschiedene Arten durchgeführt werden. Wenn Sie mehr Transistoren haben, haben Sie mehr Ressourcen, um eine schnellere Technik zu verwenden. Einige einfache Beispiele:

Bitverschiebung:

Ein einfacher Shifter wird hergestellt, indem Flip-Flops seriell miteinander verbunden werden.

Das braucht nur ein Flip-Flop pro Bit und ist daher extrem kompakt. Aber es braucht eine Uhr, um ein Bit nach links oder rechts zu verschieben. Aus diesem Grund haben Mikrocontroller und kleine eingebettete CPUs nur Anweisungen zum Verschieben um eins. Sehen

Wenn Sie mehr Transistoren ausgeben müssen, können Sie zu einem Barrel Shifter wechseln . Jetzt kann eine CPU Bits in einem einzigen Takt mit den Kosten von Hunderten oder Tausenden von Transistoren verschieben

Zusatz:

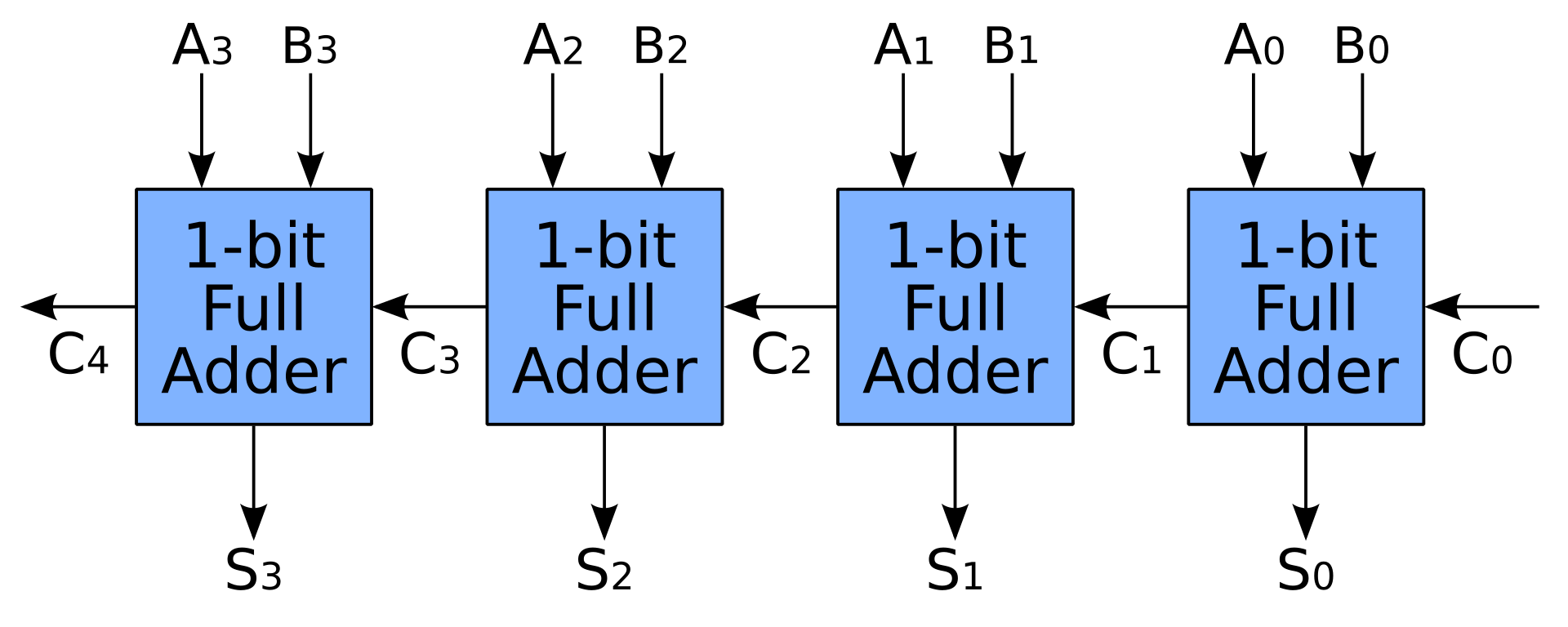

- Ein einfacher Addierer wird auch hergestellt, indem Volladdierer in Reihe geschaltet werden . Auf diese Weise benötigt ein N-Bit-Addierer N Takte, um seinen Job zu beenden, was sicherlich nicht das ist, was die Leute von einer CPU erwarten

- Mit mehr Transistoren können wir die Addition beschleunigen, indem wir die Übertragungen mit Carry-Lookahead oder Carry-Save- Addierer vorberechnen . Die Volladdierer werden immer noch verwendet, aber es wird viel mehr Platz für die Übertrag-Vorberechnungseinheit benötigt

- Ein einfacher Addierer wird auch hergestellt, indem Volladdierer in Reihe geschaltet werden . Auf diese Weise benötigt ein N-Bit-Addierer N Takte, um seinen Job zu beenden, was sicherlich nicht das ist, was die Leute von einer CPU erwarten

Das Gleiche gilt für andere Einheiten wie Multiplikatoren, Teiler, Scheduler ... Zum Beispiel können wir eine Multiplikation mit kombinatorischer Logik extrem schnell in einem einzigen Takt durchführen . Sie können einige einfache Beispiele in der Frage 3-Bit-Multiplikatoren sehen - wie funktionieren sie? . Die benötigten Transistoren wachsen jedoch auf das Quadrat der Eingangsbreiten. Daher verwenden kleine CPUs mit einem Multiplikator stattdessen sequentielle Logik , um viel Platz für den Multiplikator zu sparen:

Ältere Multiplikatorarchitekturen verwendeten einen Shifter und einen Akkumulator, um jedes Teilprodukt, häufig ein Teilprodukt pro Zyklus, zu summieren und die Geschwindigkeit gegen die Chipfläche auszutauschen. Moderne Multiplikatorarchitekturen verwenden den (modifizierten) Baugh-Wooley-Algorithmus, Wallace-Bäume oder Dadda-Multiplikatoren, um die Teilprodukte in einem einzigen Zyklus zu addieren. Die Leistung der Wallace-Baumimplementierung wird manchmal durch eine modifizierte Booth-Codierung eines der beiden Multiplikanden verbessert, wodurch die Anzahl der Teilprodukte verringert wird, die summiert werden müssen

https://en.wikipedia.org/wiki/Binary_multiplier#Implementations

Sobald Sie einen riesigen Pool an Transistoren haben, können Sie sogar kombinatorische Logik verwenden, um eine FMA zu erstellen, die weitaus ressourcenintensiver ist als ein Multiplikator

Moderne Computer können einen dedizierten MAC enthalten, der aus einem in kombinatorischer Logik implementierten Multiplikator, gefolgt von einem Addierer und einem Akkumulatorregister besteht, das das Ergebnis speichert. Der Ausgang des Registers wird zu einem Eingang des Addierers zurückgeführt, so dass bei jedem Taktzyklus der Ausgang des Multiplikators zum Register addiert wird. Kombinationsmultiplikatoren erfordern viel Logik, können jedoch ein Produkt viel schneller berechnen als die für frühere Computer typische Methode zum Verschieben und Hinzufügen.